| T O P I C R E V I E W |

| snarf |

Posted - Aug 28 2014 : 08:27:23 AM

Hi all! My first post. I built this Time Delay Relay and works OK but since I’m not able to design or modify circuits I require some help to modify this circuit.

1. The timer must be activated when 12VDC is present and not with a switch. Will reset when 12VDC in not present.

2. The relay must be energised after the time has elapsed.

I have seen Time Delay Relay II but can not try it as can’t find 4011 CMOS NAND Gate IC at local shop.

Spoon feeding please and a diagram will help me, thank you.

|

| 15 L A T E S T R E P L I E S (Newest First) |

| pebe |

Posted - Nov 08 2014 : 11:02:25 AM

I am pleased to have been of assistance, and if there is any other way I can help please come back. |

| snarf |

Posted - Oct 30 2014 : 5:15:14 PM

quote:

Re the 4060 circuit you gave a link to. I don’t know if the person who drew it up ever tested it, but it is very ‘iffey’. The cap has to charge up to half supply voltage, and polarity changes every half cycle. I think it highly unlikely that the electrolytic could reverse charge via 10K to that voltage – I think the reverse leakage current would be too high. But if it did, it would be impossible to calculate the oscillator frequency – there would be too many unknowns.

That is only one example out of many others. Unfortunately for those like myself who are trying to learn end confused as circuits like these are misleading. I was lucky that you had kindly explained the difference a while back and this made me realise the ambiguity in the circuit.

quote:

The 555 circuit doesn’t make any sense to me, and I cannot see what it is supposed to do. Are you sure you have drawn it correctly?

I have checked the circuit a couple of times and the drawn circuit I posted seems to be correct. An important point I forgot to mention is that some of the soldering on the PCB looks different from the rest of the soldering. This gives me the impression that it might have undergone some kind of repair and that might explain the wrong orientation of D2 and the connection of C2 to point ‘A’.

quote:

D2 would take pin2 voltage up with the supply rail when the circuit was first switched on. That would serve no useful purpose because pin2 is the trigger pin and it needs to go below 1/3 supply voltage to trigger the 555. I think you are right and the diode has been fitted in reverse in error.

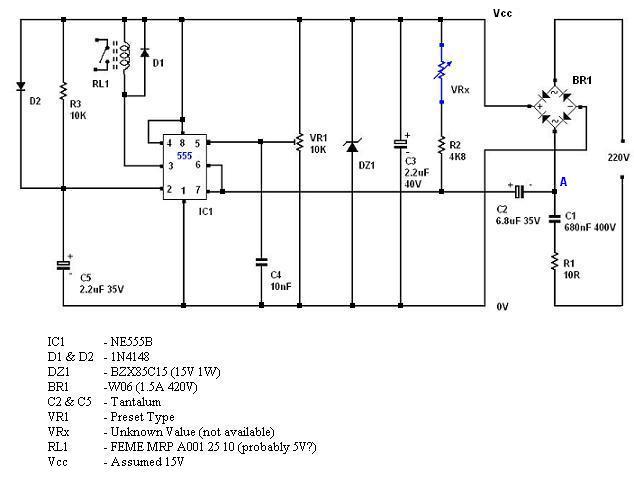

The 15V supply is obtained by using the energy in C1 each half cycle to ‘pump up’ C3. As soon as C3 reaches 15V, DZ1 will start to conduct to keep Vcc constant. Accordingly, when the relay energises and takes current, less current will go through DZ1.

Now for the rest of the circuit. Assume D2 to be correctly fitted. At switch-on C3 would be low and would trigger the 555. Pin3 would go high, keeping the relay off. Then C3 would charge up via R3 to 15V and would have no further effect on the circuit.

If the RH side of C2 were connected to 0V instead of point ‘A’, then C2 would charge and pin6 would rise to 2/3 of Vcc. At that point pin3 would go low turning on the relay and pin7 would go low discharging C2. There the operation would end, so I think the circuit is intended to delay operation of the relay for some fixed time each time the unit was switched on.

Point ‘A’ goes from –0.7V to +15.7V during a mains cycle. C2 would pass that change on to pin6 and the 555 would reset. Pin7 would switch to 0V and so an AC voltage would appear across C2, with an unknown result. So I think the C2 connection to ‘A’ is in error.

About VR1: Inside the 555 are 3 equal value resistors in series. Their two junctions provide the two reference points of 1/3Vcc and 2/3Vcc for triggering pins2 & 6. The 2/3Vcc is taken out to pin5, so varying the voltage on that pin will affect the timing. I think VRx is probably a user adjustable pot to alter the delay period, and VR1 would be factory preset to allow for the tolerances of C2, R2 and VRx.

Many thanks for your detailed explanations to my questions and circuit function, it makes more sense now.

quote:

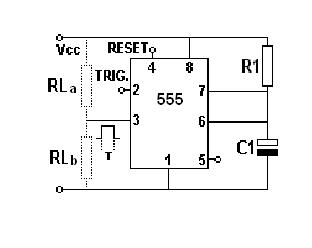

The ‘standard’ LM555 uses bipolar transistors. Pin3 is switched to 0v (output current is ‘sunk’) by an NPN transistor that switches down to within about 50mV of the 0V rail. But pin3 is lifted to Vcc (current is sourced) by two transistors in a Darlington arrangement configured as an emitter follower. There is an inherent voltage drop of at least two diodes in series, plus some extra depending on load. So with Vcc equal to 15V, pin3 would go no higher than 12.5V to 13.3V.

So there is 2V less available when using RLb rather than RLa. That has to be allowed for when deciding the voltage of the relay coil to use.

So RLb in less efficient than RLa, and there is an extra power of [2V x Load current] dissipated as heat in the 555.

The CMOS version, LCM555 has a lower maximum output current. It uses FETs for the output switches and they switch almost to 0V and Vcc, so RLa or RLb will both deliver the same voltage to the load.

OK I understand the difference between output options RLa and RLb and yes very important to always keep account of the load current.

Have read the LCM555 datasheet and although the output load current is 100mA maximum instead of the 200mA output load current for the LM555 specifications indicate that the LCM555 is more stable and accurate, lower power dissipation and oscillator frequency up to 3MHz in astable mode.

I have greatly appreciated the assistance and support given. With your (Edited : your not our) help I have managed to learn something. Many thanks to everyone in particular to Pebe who has been very patient with me and led me by the hand with his kind and detailed step by step explenations.

|

| pebe |

Posted - Oct 22 2014 : 02:22:12 AM

Re the 4060 circuit you gave a link to. I don’t know if the person who drew it up ever tested it, but it is very ‘iffey’. The cap has to charge up to half supply voltage, and polarity changes every half cycle. I think it highly unlikely that the electrolytic could reverse charge via 10K to that voltage – I think the reverse leakage current would be too high. But if it did, it would be impossible to calculate the oscillator frequency – there would be too many unknowns.

I don’t know about the BUL381D; I’ve never come across it. I see that is a high speed switching transistor used in switch mode supplies, so the diode may be there to suppress spikes when switching an inductive load. Perhaps someone else can give a more positive answer.

Thanks for the symbols – I’ll add them to my library.

The 555 circuit doesn’t make any sense to me, and I cannot see what it is supposed to do. Are you sure you have drawn it correctly?

D2 would take pin2 voltage up with the supply rail when the circuit was first switched on. That would serve no useful purpose because pin2 is the trigger pin and it needs to go below 1/3 supply voltage to trigger the 555. I think you are right and the diode has been fitted in reverse in error.

The 15V supply is obtained by using the energy in C1 each half cycle to ‘pump up’ C3. As soon as C3 reaches 15V, DZ1 will start to conduct to keep Vcc constant. Accordingly, when the relay energises and takes current, less current will go through DZ1.

Now for the rest of the circuit. Assume D2 to be correctly fitted. At switch-on C3 would be low and would trigger the 555. Pin3 would go high, keeping the relay off. Then C3 would charge up via R3 to 15V and would have no further effect on the circuit.

If the RH side of C2 were connected to 0V instead of point ‘A’, then C2 would charge and pin6 would rise to 2/3 of Vcc. At that point pin3 would go low turning on the relay and pin7 would go low discharging C2. There the operation would end, so I think the circuit is intended to delay operation of the relay for some fixed time each time the unit was switched on.

Point ‘A’ goes from –0.7V to +15.7V during a mains cycle. C2 would pass that change on to pin6 and the 555 would reset. Pin7 would switch to 0V and so an AC voltage would appear across C2, with an unknown result. So I think the C2 connection to ‘A’ is in error.

About VR1: Inside the 555 are 3 equal value resistors in series. Their two junctions provide the two reference points of 1/3Vcc and 2/3Vcc for triggering pins2 & 6. The 2/3Vcc is taken out to pin5, so varying the voltage on that pin will affect the timing. I think VRx is probably a user adjustable pot to alter the delay period, and VR1 would be factory preset to allow for the tolerances of C2, R2 and VRx.

quote:

General 555 question.

The output form a 555 IC can be taken from either pin 3 to Vcc rail (RLa), or pin 3 to GND rail (RLb).

Apart from the opposite output function of both options is it advisable to opt for (RLb) configuration or it does not make any difference?

Is it true that the 555 IC is more loaded with an (RLa) configuration and heats up more?

The ‘standard’ LM555 uses bipolar transistors. Pin3 is switched to 0v (output current is ‘sunk’) by an NPN transistor that switches down to within about 50mV of the 0V rail. But pin3 is lifted to Vcc (current is sourced) by two transistors in a Darlington arrangement configured as an emitter follower. There is an inherent voltage drop of at least two diodes in series, plus some extra depending on load. So with Vcc equal to 15V, pin3 would go no higher than 12.5V to 13.3V.

So there is 2V less available when using RLb rather than RLa. That has to be allowed for when deciding the voltage of the relay coil to use.

So RLb in less efficient than RLa, and there is an extra power of [2V x Load current] dissipated as heat in the 555.

The CMOS version, LCM555 has a lower maximum output current. It uses FETs for the output switches and they switch almost to 0V and Vcc, so RLa or RLb will both deliver the same voltage to the load.

|

| snarf |

Posted - Oct 19 2014 : 5:40:50 PM

Thank you for your detailed reply.

quote:

Both have good insulation and low equivalent series resistance so both can be used for timing circuit. But tantalum capacitors are normally polarised, which means they cannot be used as the timing component in any oscillator where polarity of the cap changes every half cycle – typically one made from gates as in the CD4060 you have just used.

From your previous explanations I did understand that polarised capacitors such as tantalums can not be used with the CD4060 or similar, but thank you for pointing it out again. My question was for a comparison of the two different types of capacitors and your reply also explains it, thank you.

What I don’t understand is why some CD4060 circuits are using polarised capacitors like the circuit found here.

http://www.coolcircuit.com/circuit/timer_4060/

quote:

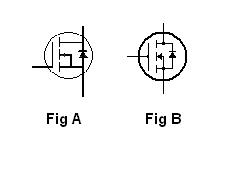

I didn’t realise both symbols were present. I made that file up by copying symbols used in other people's circuits and hadn’t realized I had duplicates. They are both the same and you can delete one of them.

They show an N channel IGFET with an inbuilt zener to provide clamping when driving inductive loads. If you look up the data sheet for an IRF530 it will tell you more about it.

Thank you for explaining. The IGFET is new for me. It was the diode symbol in both Fig A and Fig B, and the missing arrow which indicates the type of channel in Fig A that confused me, so I thought it’s better to ask.

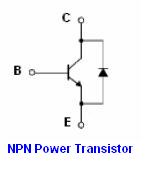

From your explanation I learned that some Power Transistors like the BUL381D also have a similar protection diode integrated, called the “antiparallel collector-emitter diode” , but this is a diode and not a Zener diode, is that right?

Download Attachment:  NPN Power Transistor.JPG NPN Power Transistor.JPG

4.12 KB

I have come across a collection of high quality symbols which may be useful. They can be downloaded from here.

http://www.circuitstune.com/2012/07/electrical-schematic-symbols.html

quote:

For more information about electronics, you may find this website interesting. It contains some very useful information

http://www.electronics-tutorials.ws

Many thanks for the link, very useful to me.

I have found a used and damaged 555 timer which has a broken relay and PCB. I could not test it but managed to draw a circuit.

Download Attachment:  555 CCT QST.JPG 555 CCT QST.JPG

37.4 KB

I am not understanding the circuit fully can you please help with some explanations?

1. From what I understand the timing RC are VRx + R2 and C2. Why is C2 connected to the AC source (marked A in diagram) instead of being connected to 0V (GND)? Is it using the mains 50Hz and why?

2. Capacitor C1 (680nF) should provide a continuous current of approximately 45mA, which I would assume is required to operate the circuit and the relay. When the relay is not energised the circuit will not require all that current but C1 still gives the same current, so where does the excess current go?

3. Why is the circuit using voltage control (VR1)? I assume Vcc to be +15V, why not use a lower Vcc instead of using voltage control (VR1), or is VR1 also dissipating the excess current?

4. Should D2 discharge C5 when power is switched off? If yes D2’s direction should be opposite, right?

General 555 question.

Download Attachment:  555 Load.JPG 555 Load.JPG

10.67 KB

The output form a 555 IC can be taken from either pin 3 to Vcc rail (RLa), or pin 3 to GND rail (RLb).

Apart from the opposite output function of both options is it advisable to opt for (RLb) configuration or it does not make any difference?

Is it true that the 555 IC is more loaded with an (RLa) configuration and heats up more?

|

| pebe |

Posted - Oct 17 2014 : 12:14:19 PM

quote:

I am aware that tantalum capacitors are more expensive and that common tantalum capacitance values available range from 0.047µF (47nF) to around 680µF, but since tantalum are also ideal for timing purposes how do tantalum compeer with polys?

Both have good insulation and low equivalent series resistance so both can be used for timing circuit. But tantalum capacitors are normally polarised, which means they cannot be used as the timing component in any oscillator where polarity of the cap changes every half cycle – typically one made from gates as in the CD4060 you have just used. Polys there are a must. Tants can be used in other oscillators where polarity does not change, ie. in a 555 where the cap just charges and discharges, and when size is an important consideration.

They can also be used at either side of a voltage regulator, where typically 0.22µF is needed for filtering. The tant’s small size and low ESR score in its favour here. However they are not good for use in filtering power supplies where high ripple is present.

quote:

The file containing circuit symbols, which you kindly provided, contains two symbols that I am not familiar with, these are Fig A and Fig B. I have tried searching on the internet without finding an answer. Could you please indicate to which type of transistor these symbols refer to?

I didn’t realise both symbols were present. I made that file up by copying symbols used in other people's circuits and hadn’t realized I had duplicates. They are both the same and you can delete one of them.

They show an N channel IGFET with an inbuilt zener to provide clamping when driving inductive loads. If you look up the data sheet for an IRF530 it will tell you more about it.

For more information about electronics, you may find this website interesting. It contains some very useful information

http://www.electronics-tutorials.ws

|

| snarf |

Posted - Oct 14 2014 : 1:31:55 PM

Thank you for your reply and sorry for my late response.

quote:

I only use ceramics for the smaller capacities for RF work.

For coupling or decoupling where stability is not important then the larger ceramics would be OK, but their temperature coefficient is too large to use them for timing purposes. They are also usually more expensive than polys so for all these purposes I use polyester or polycarbonate types exclusively.

OK understood.

I am aware that tantalum capacitors are more expensive and that common tantalum capacitance values available range from 0.047µF (47nF) to around 680µF, but since tantalum are also ideal for timing purposes how do tantalum compeer with polys?

quote:

Yes, you can add a resistor in parallel with the capacitor. It discharges the cap .......

Thanks for detailed explanation, helps me understand and learn how to calculate the capacitor discharge value after a time period. Most appreciated.

Download Attachment:  Image 4.JPG Image 4.JPG

5.33 KB

The file containing circuit symbols, which you kindly provided, contains two symbols that I am not familiar with, these are Fig A and Fig B. I have tried searching on the internet without finding an answer. Could you please indicate to which type of transistor these symbols refer to?

|

| pebe |

Posted - Oct 10 2014 : 09:07:24 AM

quote:

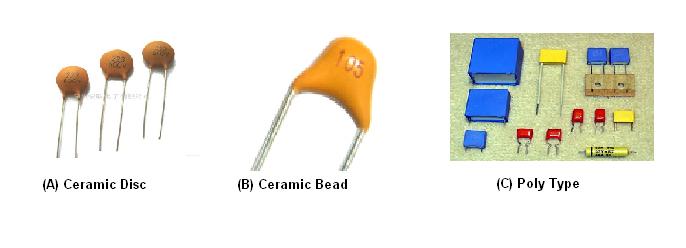

Therefore if I understand properly a ‘High K’ or multilayer ceramic will manifest a capacitance change with a voltage or temperature change?

Do the images refer to the correct type of capacitors?

So image ‘B’ is the ‘High K’ multilayer ceramic, right?

So when using non polarized capacitors for timing it’s better to use poly capacitors, right?The ‘polys’ are slightly cheaper here as well.

Therefore using your last circuit as an example C2 and C3 would preferable be poly capacitors and C1 and C5 can be either ceramic or poly capacitors, is that right?

Your assumptions are all correct.

quote:

Therefore from your explanation I would understand that it’s better to use ‘polys’ also for other applications, I am always in difficulty when it comes to non polarized capacitors, is there a simple guide line?

I only use ceramics for the smaller capacities for RF work.

For coupling or decoupling where stability is not important then the larger ceramics would be OK, but their temperature coefficient is too large to use them for timing purposes. They are also usually more expensive than polys so for all these purposes I use polyester or polycarbonate types exclusively.

quote:

When the circuit is switched OFF with C4 (100µF 25V) the charge in C4 takes a considerable time (about 15 to 20 seconds) to discharge to about 4V. If C4 is replace by a lower capacitance value, lets say 10µF 25V obviously the discharge time is much lower (about 5 seconds).

How can the charge in a capacitor be discharged quickly and safely without interfering with the capacitor’s function in the circuit? Do we add a resistor in parallel with the capacitor? If yes how do we calculate the value of the resistor?

Yes, you can add a resistor in parallel with the capacitor. It discharges the cap quickly at first because there is max volts across the resistor. As the voltage drops, the current through the resistor also drops and the cap discharges at a slower rate. So the resulting discharge curve is an exponential one.

You can calculate the voltage across the capacitor quite easily.

The ‘Time Constant’ of a resistor/capacitor combination (either in series or in parallel) is the product of capacity (in Farads) and resistance (in Ohms). You get the same result with the easier-to-use combination of microfarads and megohms. Now to calculate:

Remaining voltage across cap (as a proportion) = natural log to the power of minus (time / time constant.)

So remaining V = e^ -(T/TC)

If you use 10µF and 100K, the TC = 1sec, so the proportion of initial voltage remaining will be:

After 1.0sec e^ -1.0 = .368

After 1.5sec e^ -1.5 = .223

After 2.0sec e^ -2.0 = .135

After 2.5sec e^ -2.5 = .082

After 3.0sec e^ -3.0 = .049

After 4.0sec e^ -4.0 = .018

After 5.0sec e^ -5.0 = .006

So from this you can work out that if you choose 10µF and 100K, then after 4secs the cap will have discharged down to 1.8% of its original voltage.

I hope that all makes sense.

|

| snarf |

Posted - Oct 08 2014 : 3:38:59 PM

quote:

Your Fig 1 is correct –my Fig 2 is wrong. Sorry about that. I must try to remember, “More haste – less speed”

That’s OK no problem, resolving difficulties helps me to learn. I always try hard to find the solution on my own first and ask only when I end with my back against the wall or when I’m not so sure with my conclusions .

quote:

It can be done, but my original circuit will need some changes, so I have now amended it. Here are the changes:

C5……………………

Thank you so much for the new circuit and your in depth and detailed explanations which help me to understand and learn at the same time. Assembled on breadboard and tried out. Works to perfection and without problems, again many thanks.

The circuit is now more versatile, flexible and standalone, this makes it possible to use in other applications if required.

quote:

quote:

________________________________________

……… Can we take the output from Q14 of IC2 and feed it to pin 11 of IC1 maybe with a diode to drive IC1 pin 11 high, and modify the IC’s counter resetting to reset only IC2?

If……………………

________________________________________

Although I was a bit off track I think that in a way my reasoning was in the right direction. Credit is all due to your kind and detailed explanations. From your circuit I can now see what I didn’t take into consideration and where I went wrong.

quote:

quote:

________________________________________

We had D1 removed from the circuit because it was not needed. For the sake of learning did D1 have any particular function or just not required?

________________________________________

In my first circuit it was put in to stop IC1. On reflection I thought it would not be needed because IC1 Q14 only stayed high for 10secs before IC2 output reset both counters via R3……………

I understood that D1 was to stop IC1 from counting further as you had already explained that before I posted my 4060 5sec + 5sec circuit, but since both IC’s are being reset when IC2 – Q14 goes high, stopping IC1 does not make much difference in that particular circuit (bearing in mind that the relay is switching OFF the timer’s circuit power). So I thought that is why D1 can be removed, or maybe D1 has a dual function that I’m not understanding. Therefore I decided to ask to have things clear in my mind. Thanks for the explanation.

quote:

quote:

________________________________________

Therefore it’s best to use ‘poly’ capacitors and not ‘ceramic’ capacitors because ‘ceramic’ capacitors have a higher internal resistance?

________________________________________

No, it’s a question of stability at varying temperatures. Small ceramics up to about 100pF are very stable, but when you get up to 100nF you have to use a ‘High K’ or a multiplayer ceramic. Neither of these is as stable as a polyester or a polystyrene cap. Although that doesn’t matter for decoupling caps it does matter if you are using them as timing caps. So when it comes to stocking caps for multi purposes, it pays to stock ‘polys’ rather than ceramics, and where I get my supplies from they are cheaper.

I have been reading;

http://www.edn.com/design/analog/4416466/Signal-distortion-from-high-K-ceramic-capacitors

and

http://www.edn.com/design/analog/4426318/More-about-understanding-the-distortion-mechanism-of-high-K-MLCCs

Therefore if I understand properly a ‘High K’ or multilayer ceramic will manifest a capacitance change with a voltage or temperature change?

Download Attachment:  Image 3.JPG Image 3.JPG

17.92 KB

Do the images refer to the correct type of capacitors?

So image ‘B’ is the ‘High K’ multilayer ceramic, right?

So when using non polarized capacitors for timing it’s better to use poly capacitors, right?

Therefore from your explanation I would understand that it’s better to use ‘polys’ also for other applications, I am always in difficulty when it comes to non polarized capacitors, is there a simple guide line?

The ‘polys’ are slightly cheaper here as well.

Therefore using your last circuit as an example C2 and C3 would preferable be poly capacitors and C1 and C5 can be either ceramic or poly capacitors, is that right?

This question refers to C4 in your last circuit but is only intended for my learning.

When the circuit is switched OFF with C4 (100µF 25V) the charge in C4 takes a considerable time (about 15 to 20 seconds) to discharge to about 4V. If C4 is replace by a lower capacitance value, lets say 10µF 25V obviously the discharge time is much lower (about 5 seconds).

How can the charge in a capacitor be discharged quickly and safely without interfering with the capacitor’s function in the circuit? Do we add a resistor in parallel with the capacitor? If yes how do we calculate the value of the resistor?

|

| pebe |

Posted - Oct 07 2014 : 08:14:33 AM

quote:

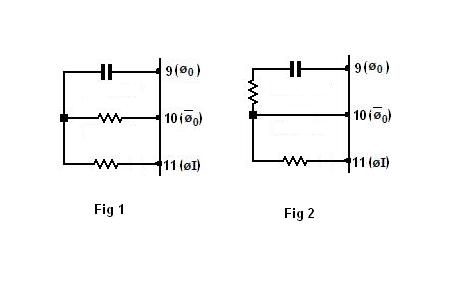

The RC circuit in the 2 by 4060s circuit is represented by Fig 2. The timer circuit did not function with this RC configuration. Therefore I changed the RC configuration as represented in Fig 1 and the timer circuit functioned properly. I’m a bit confused can you please explain?

Your Fig 1 is correct –my Fig 2 is wrong. Sorry about that. I must try to remember, “More haste – less speed”

quote:

Understood, and I have been trying to figure out how it can be done in the 2 by 4060s circuit. Can we take the output from Q14 of IC2 and feed it to pin 11 of IC1 maybe with a diode to drive IC1 pin 11 high, and modify the IC’s counter resetting to reset only IC2?

If it’s the wrong approach please explain how to make pin 11 of IC1 go low or high when the 5 seconds pulse ends.

It can be done, but my original circuit will need some changes, so I have now amended it. Here are the changes:

C5 now added and D1 has been restored. VR2 value has been changed, and R3 now connects to 0V instead of to Q14 output.

Now IC1 counts as before but at the end of its count when Q14 goes high, D1 conducts and pulls up pin11 to prevent it counting further. So Q14 stays high. Q14 going high makes D2 reverse biased and so non-conductive. D3 is reversed biased so there is now no control over pin 11 and IC2 counter starts (note that taking pin 11 either high or low will stop the oscillator).

As D3 anode has to be taken high to stop IC2, it is now fed from Q14 output. The 5sec timed output now comes from Q13, so the oscillator has to run at half its original speed. This can be done either by a) increasing VR2 to 47K as shown, or b) adding a 15K to 22K fixed resistor in series with VR2, or c) changing C3 to 22nF. Use whichever method is best for you.

Now with its oscillator running at half speed, Q13 will go high 5secs after the count starts and will give an output (after a total delay of 295 + 5secs). After a further 5secs Q14 will go high, turning on D3 and stopping the oscillator. At the same time Q13 will go low, ending the output. Both counters will stay in that position until the 12V supply is removed.

R4 is added to prevent D3 and D4 conducting if IC1 Q14 goes low and IC2 Q14 goes high together. It should never happen but R4 is there in case.

quote:

Therefore it’s best to use ‘poly’ capacitors and not ‘ceramic’ capacitors because ‘ceramic’ capacitors have a higher internal resistance?

No, it’s a question of stability at varying temperatures. Small ceramics up to about 100pF are very stable, but when you get up to 100nF you have to use a ‘High K’ or a multiplayer ceramic. Neither of these is as stable as a polyester or a polystyrene cap. Although that doesn’t matter for decoupling caps it does matter if you are using them as timing caps. So when it comes to stocking caps for multi purposes, it pays to stock ‘polys’ rather than ceramics, and where I get my supplies from they are cheaper.

quote:

We had D1 removed from the circuit because it was not needed. For the sake of learning did D1 have any particular function or just not required?

In my first circuit it was put in to stop IC1. On reflection I thought it would not be needed because IC1 Q14 only stayed high for 10secs before IC2 output reset both counters via R3. Now, it is necessary to stop IC1 with D1 or else Q14 will toggle up and down every 295secs Q14, clocking IC2 as it does so.

I hope I have explained things well enough.

Download Attachment:  4060-2.GIF 4060-2.GIF

16.73 KB

|

| snarf |

Posted - Oct 06 2014 : 1:07:42 PM

Both 4060 circuits have been assembled on a breadboard and tried out. I refer to the revised circuit I posted and Pebe’s 2 by 4060s circuit. The circuits functioned as Pebe outlined but I had some difficulty with the 2 by 4060s circuit as outlined below.

Please explain the difference between the RC circuits represented by Fig 1 and Fig 2.

Download Attachment:  Image 2.JPG Image 2.JPG

10.42 KB

The RC circuit in the 2 by 4060s circuit is represented by Fig 2. The timer circuit did not function with this RC configuration. Therefore I changed the RC configuration as represented in Fig 1 and the timer circuit functioned properly. I’m a bit confused can you please explain?

quote:

quote:

________________________________________

OK I understand but just for the sake of learning something else can the circuit be stopped from repeating, similar to what happens in the 2 by 555’s circuit?

________________________________________

The oscillator cannot run without a power supply, but assuming there was power, then taking pin11 of IC1 high or low would stop its oscillator. With its Q14 low there is no way either of the ICs could count.

Understood, and I have been trying to figure out how it can be done in the 2 by 4060s circuit. Can we take the output from Q14 of IC2 and feed it to pin 11 of IC1 maybe with a diode to drive IC1 pin 11 high, and modify the IC’s counter resetting to reset only IC2?

If it’s the wrong approach please explain how to make pin 11 of IC1 go low or high when the 5 seconds pulse ends.

quote:

I will try to explain. If you look at the data sheet for the 4060, it shows a block diagram of what is inside the IC. It consists of an oscillator driving a number of ÷2 counters. The output of each counter consists of a complimentary pair of FETs; one switches the output to Vdd and the other switches it to Vss, as appropriate. As the output changes over, there is a very brief period when both FETs are switched on together and so they create a low resistance across the supply. The result is a brief increase in supply current that tends to lower the voltage between Vdd and Vss.

The wiring from the power supply to the ICs has inherent inductance that will try to prevent this increased current and so Vdd would drop during these very short pulses. In addition, the electrolytic cap used to smooth the supply will also have an inherent series resistance, so it will not effectively provide the short pulses of current necessary to maintain Vdd.

The answer is to use one of the ‘poly’ capacitors that have very low internal resistance across the supply, mounted as close as possible to the ICs to avoid the supply line inductance effects. Provided both ICs are fairly close to one another, then a single 100nF will be sufficient.

Thank you for the detailed explanation. As you may have noted I do read data sheets but that does not mean that I understand everything explained in the data sheets. Please remember that my knowledge and experience are very limited.

Therefore it’s best to use ‘poly’ capacitors and not ‘ceramic’ capacitors because ‘ceramic’ capacitors have a higher internal resistance?

For my breadboard trial I used two 100nF capacitors as on the breadboard it was difficult to mount the ICs close to one another.

quote:

At startup, C1 is discharged and puts a high on the resets of both ICs, resetting them. IC1-Q14 is low so there is no output. D2 pulls down pin11 of IC2 and stops its oscillator. IC2-Q14 is low and via R3 charges C1 to take off the reset. D1 is reverse biased so has no effect on IC1-pin11, so it starts to count.

We had D1 removed from the circuit because it was not needed. For the sake of learning did D1 have any particular function or just not required?

|

| pebe |

Posted - Oct 05 2014 : 08:22:45 AM

quote:

OK I understand but just for the sake of learning something else can the circuit be stopped from repeating, similar to what happens in the 2 by 555’s circuit?

The oscillator cannot run without a power supply, but assuming there was power, then taking pin11 of IC1 high or low would stop its oscillator. With its Q14 low there is no way either of the ICs could count.

quote:

OK but if I leave C4 at 100µF it should still be alright?

Yes, no problem.

quote:

Sorry I’m not sure if I understand, you mean one 100nF capacitor between +12V and 0V for each IC or only one 100nF for both IC’s? That would mean in parallel with C4, right?

and

I don't understand what you mean by “near pins 8 and 16” ? The pins are physically opposite each other and if it’s only one 100nF capacitor that needs adding near which IC should I add it?

I will try to explain. If you look at the data sheet for the 4060, it shows a block diagram of what is inside the IC. It consists of an oscillator driving a number of ÷2 counters. The output of each counter consists of a complimentary pair of FETs; one switches the output to Vdd and the other switches it to Vss, as appropriate. As the output changes over, there is a very brief period when both FETs are switched on together and so they create a low resistance across the supply. The result is a brief increase in supply current that tends to lower the voltage between Vdd and Vss.

The wiring from the power supply to the ICs has inherent inductance that will try to prevent this increased current and so Vdd would drop during these very short pulses. In addition, the electrolytic cap used to smooth the supply will also have an inherent series resistance, so it will not effectively provide the short pulses of current necessary to maintain Vdd.

The answer is to use one of the ‘poly’ capacitors that have very low internal resistance across the supply, mounted as close as possible to the ICs to avoid the supply line inductance effects. Provided both ICs are fairly close to one another, then a single 100nF will be sufficient.

I hope that explains it OK.

|

| snarf |

Posted - Oct 04 2014 : 4:40:16 PM

quote:

quote:

________________________________________

quote:”Does the 5sec pulse turn it off? If not, what is the ‘control’ that turns it off?”

Yes it does, when the 5 seconds pulse STARTS the relay is turned ON and when the 5 seconds pulse ENDS the relay is turned OFF. Thereby one set of relay contacts will be turning the timer’s circuit Power OFF, remember the relay contacts bridging the so called S1.

________________________________________

I can see how the relay operates. My question was: how is the 240V mains turned off?

Sorry I misunderstood. During the 5 seconds pulse the indicated LOAD will be switched ON. This LOAD circuit is controlled by a contactor which we can say also controls the 240V mains to the other electrical circuit (the so called switch S1). Therefore the timer relay will switch ON the LOAD contactor (for those 5 seconds pulse) giving power (240V) to the LOAD and at the same time this LOAD contactor switches OFF the 240V mains to the other electrical circuit (the so called switch S1) thereby resetting the electrical circuit and it’s output to the timer circuit is also switched OFF.

Therefore when the timer cycle ENDS and the timer relay is switched OFF the timer circuit has NO power, so it’s switched OFF. At the same time the LOAD contactor is also being switched OFF by the timer relay. With the LOAD contactor switched OFF the electrical circuit (the so called switch S1) again has power (240V) but it’s not active (not giving an output). The timer circuit will be switched ON again when the electrical circuit (the so called switch S1) again becomes active (gives an output) due to meeting one of the electrical circuit conditions in which case the process repeats again.

quote:

quote:

________________________________________

Your assumptions are correct, one set of relay contacts will be taking the Power OFF, therefore it should not repeat. But if it does maybe because the timer circuit resets before the relay physically turns OFF (electro mechanical is slower compared with electronic), can a diode (similar to what we had in the 4060 5sec by 5sec circuit) be included to stop the counter from repeating until the relay has turned OFF?

________________________________________

When the relay turns off the power, the two ICs will have been reset, so even if the power does not go off immediately and the counters start again, it will take 300secs before the relay can switch on again.

OK I understand but just for the sake of learning something else can the circuit be stopped from repeating, similar to what happens in the 2 by 555’s circuit?

quote:

quote:

________________________________________

When I posted my revised circuit I forgot to include the 100µF capacitor across the DC source, sorry for the omission.

________________________________________

As there is no interruption of the supply voltage during both counts, you can reduce the 100µF cap across the supply to 10µF min.

OK but if I leave C4 at 100µF it should still be alright?

quote:

But as both oscillators are running during the 5sec time, add a 100nF cap across supply near pins 8 and 16 to prevent common coupling between them due to short spikes on the supply rail.

Sorry I’m not sure if I understand, you mean one 100nF capacitor between +12V and 0V for each IC or only one 100nF for both IC’s? That would mean in parallel with C4, right?

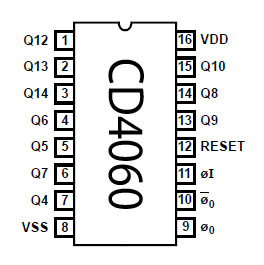

Download Attachment:  CD4060-CMOS-pinout.jpg CD4060-CMOS-pinout.jpg

27.8 KB

I don't understand what you mean by “near pins 8 and 16” ? The pins are physically opposite each other and if it’s only one 100nF capacitor that needs adding near which IC should I add it?

I got the 4060’s today, I will do my best to assemble tomorrow and hopefully post by latest on Monday.

|

| pebe |

Posted - Oct 03 2014 : 5:14:20 PM

quote:

quote:”Does the 5sec pulse turn it off? If not, what is the ‘control’ that turns it off?”

Yes it does, when the 5 seconds pulse STARTS the relay is turned ON and when the 5 seconds pulse ENDS the relay is turned OFF. Thereby one set of relay contacts will be turning the timer’s circuit Power OFF, remember the relay contacts bridging the so called S1.

I can see how the relay operates. My question was: how is the 240V mains turned off?

quote:

Your assumptions are correct, one set of relay contacts will be taking the Power OFF, therefore it should not repeat. But if it does maybe because the timer circuit resets before the relay physically turns OFF (electro mechanical is slower compared with electronic), can a diode (similar to what we had in the 4060 5sec by 5sec circuit) be included to stop the counter from repeating until the relay has turned OFF?

When the relay turns off the power, the two ICs will have been reset, so even if the power does not go off immediately and the counters start again, it will take 300secs before the relay can switch on again.

quote:

When I posted my revised circuit I forgot to include the 100µF capacitor across the DC source, sorry for the omission.

As there is no interruption of the supply voltage during both counts, you can reduce the 100µF cap across the supply to 10µF min. But as both oscillators are running during the 5sec time, add a 100nF cap across supply near pins 8 and 16 to prevent common coupling between them due to short spikes on the supply rail.

|

| snarf |

Posted - Oct 02 2014 : 12:29:36 PM

Sorry for late reply.

quote:

Does the 5sec pulse turn it off? If not, what is the ‘control’ that turns it off?

Yes it does, when the 5 seconds pulse STARTS the relay is turned ON and when the 5 seconds pulse ENDS the relay is turned OFF. Thereby one set of relay contacts will be turning the timer’s circuit Power OFF, remember the relay contacts bridging the so called S1.

quote:

OK, I’ll draw up a circuit. It is a simple circuit but will require 2 x 4060s.

quote:

It cannot be done with a single 4060. I could have given you a circuit that used one 4060 and one 4082 dual AND, but the gating was messy and you could not adjust the times individually. So here is the circuit with two 4060s.

Thank you so much for both the circuit and detailed circuit explanation. I should have the 4060 in hand tomorrow or Saturday and then first I will assemble the circuit on a breadboard, after which I will get back with a reply.

I could have never managed to make this circuit myself, maybe in time, thanks again.

quote:

With this circuit each of the times can be individually set by the VR pots. IC1 is the 300sec delay timer. IC2 is the 5sec timer.

Agreed, it’s always better to have individual time settings.

quote:

I assume the relay contact takes the power off so the counters cannot repeat.

Your assumptions are correct, one set of relay contacts will be taking the Power OFF, therefore it should not repeat. But if it does maybe because the timer circuit resets before the relay physically turns OFF (electro mechanical is slower compared with electronic), can a diode (similar to what we had in the 4060 5sec by 5sec circuit) be included to stop the counter from repeating until the relay has turned OFF?

quote:

(Edit) You don't need D1, so leave it out.

OK no problem, but what would have been the function of D1?

When I posted my revised circuit I forgot to include the 100µF capacitor across the DC source, sorry for the omission.

|

| pebe |

Posted - Oct 01 2014 : 2:52:39 PM

It cannot be done with a single 4060. I could have given you a circuit that used one 4060 and one 4082 dual AND, but the gating was messy and you could not adjust the times individually. So here is the circuit with two 4060s. With this circuit each of the times can be individually set by the VR pots. IC1 is the 300sec delay timer. IC2 is the 5sec timer.

At startup, C1 is discharged and puts a high on the resets of both ICs, resetting them. IC1-Q14 is low so there is no output. D2 pulls down pin11 of IC2 and stops its oscillator. IC2-Q14 is low and via R3 charges C1 to take off the reset. D1 is reverse biased so has no effect on IC1-pin11, so it starts to count.

After 300secs IC1-Q14 will go high and there is now an output. D2 is now reverse biased so IC2 will start to count. After a further 5secs, IC2-Q14 will go high taking the resets high and resetting both counters and taking all Qs and the output low.

So when the ICs are powered up, there will be a delay of 300secs with no output. Then the output will go high for 5secs and then low again. I assume the relay contact takes the power off so the counters cannot repeat.

I hope you find that to be OK.

(Edit) You don't need D1, so leave it out.

Download Attachment:  4060.GIF 4060.GIF

15.64 KB

|

|

|